IBM kondigt nieuw onderzoek aan in opticatechnologie dat de efficiëntie en prestaties van datacenters bij het trainen en uitvoeren van generative AI-modellen ingrijpend kan verbeteren. Onderzoekers hebben een innovatief proces ontwikkeld voor co-packaged optica (CPO), de volgende generatie opticatechnologie, die verbindingen in datacenters met de snelheid van licht mogelijk maakt en bestaande elektrische verbindingen op korte afstand aanvult.

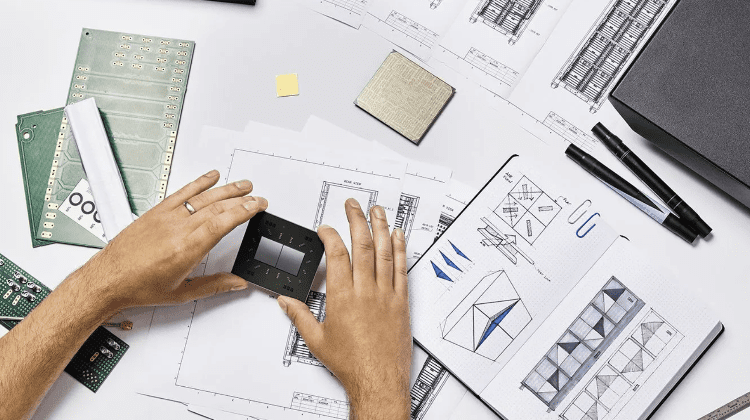

Met de ontwikkeling en assemblage van de eerste succesvolle polymeren optische golfgeleider (Polymer Optical Waveguide, PWG) laat IBM zien hoe CPO de gegevensoverdracht met hoge bandbreedte tussen chips, printplaten en servers in de computerindustrie fundamenteel zal herdefiniëren.

Glasvezeltechnologie maakt tegenwoordig snelle datatransmissie over lange afstanden mogelijk door gebruik te maken van licht in plaats van elektriciteit. Hoewel datacenters glasvezel inzetten voor externe communicatie, vertrouwen de interne racks binnen datacenters grotendeels nog op koper-gebaseerde elektrische bedrading. Deze bedrading verbindt GPU-accelerators, die vaak meer dan de helft van de tijd inactief blijven terwijl ze wachten op gegevens van andere apparaten tijdens omvangrijke, gedistribueerde trainingsprocessen. Dit leidt tot aanzienlijke kosten en een hoog energieverbruik.

De onderzoekers hebben aangetoond hoe de snelheid en capaciteit van optische technologie kan worden geïntegreerd in de interne werking van datacenters. IBM introduceert een prototype van een CPO-module (Co-Packaged Optics) die hoge-snelheids optische connectiviteit mogelijk maakt. Deze technologie kan de bandbreedte van datacentercommunicatie aanzienlijk verhogen, de inactiviteit van GPU’s minimaliseren en de verwerking van AI drastisch versnellen.

De voordelen van de nieuwe CPO-technologie:

- Lagere kosten voor het opschalen van generative AI, dankzij een meer dan vijfvoudige vermindering van het energieverbruik in vergelijking met elektrische verbindingen op middellange afstand, en een verlenging van de kabellengte in datacenters van enkele meters tot honderden meters.

- Snellere AI-modeltraining, waarbij developers een Large Language Model (LLM) tot vijf keer sneller kunnen trainen met CPO dan met conventionele elektrische bedrading. Dit kan de tijd voor het trainen van een standaard LLM verkorten van drie maanden tot drie weken, met grotere prestatievoordelen bij gebruik van grotere modellen en meer GPU’s.

- Snellere training van AI-modellen, met CPO kunnen developers een Large Language Model (LLM) tot vijf keer sneller trainen dan met traditionele elektrische bedrading. Hierdoor kan de trainingstijd van een standaard LLM worden verkort van drie maanden naar drie weken, met nog meer voordelen bij grotere modellen en meer GPU’s.

- Verbeterde energie-efficiëntie voor datacenters, waardoor energie wordt bespaard die gelijk is aan het jaarlijkse elektriciteitsverbruik van 5000 huishoudens per getraind AI-model.

“Generatieve AI vraagt om steeds meer energie en rekenkracht, waardoor datacenters moeten evolueren. Co-packaged optica kan deze datacenters toekomstbestendig maken”, zegt Dario Gil, Senior Vice President en director research bij IBM. “Met deze doorbraak zullen de chips van morgen communiceren zoals glasvezelkabels nu data in en uit datacenters transporteren. Dit markeert het begin van een nieuw tijdperk van snellere, duurzamere communicatie die de AI-workloads van de toekomst aankan.”

Tachtig keer snellere bandbreedte dan huidige chip-to-chipcommunicatie

Recente vooruitgangen in chiptechnologie hebben geleid tot een hogere transistorendichtheid op chips, waarbij de 2 nanometer node-chiptechnologie van IBM meer dan 50 miljard transistors kan bevatten. CPO-technologie heeft tot doel de verbindingsdichtheid tussen accelerators te verhogen door chipmakers in staat te stellen optische verbindingen toe te voegen die chips op een elektronisch module verbinden, voorbij de beperkingen van de huidige elektrische verbindingen.

IBM heeft aangetoond hoe nieuwe optische structuren met hoge bandbreedtedichtheid, gecombineerd met het gebruik van meerdere golflengtes per optisch kanaal, de bandbreedte tussen chips tot wel 80 keer kunnen vergroten in vergelijking met elektrische verbindingen. IBM’s innovatie maakt het mogelijk om zes keer zoveel optische vezels aan de rand van een siliconen-fotonicschip toe te voegen, wat wordt aangeduid als ‘beachfront density’, vergeleken met de huidige stand van de techniek in CPO-technologie. Elke vezel, die ongeveer drie keer zo breed is als een mensenhaar, kan lengtes van centimeters tot honderden meters beslaan en terabits aan data per seconde overdragen. Het IBM-team heeft een PWG met hoge dichtheid geassembleerd op optische kanalen met een pitch van 50 micrometer, adiabatisch gekoppeld aan siliconen-fotonics-golflengtes, gebruikmakend van standaard assemblageverpakkingsprocessen.

Daarnaast heeft IBM aangetoond dat deze CPO-modules met PWG op een pitch van 50 micrometer de eerste zijn die alle stress tests hebben doorstaan die nodig zijn voor de productie. De componenten werden getest in omgevingen met hoge luchtvochtigheid en temperaturen variërend van ‑40°C tot 125°C en ondergingen mechanische duurzaamheidstests om te verifiëren dat de optische verbindingen kunnen buigen zonder te breken of gegevens te verliezen. Bovendien heeft het onderzoek aangetoond dat PWG-technologie met een pitch van 18 micrometer mogelijk is. Door vier PWG’s te stapelen, kunnen tot 128 kanalen voor connectiviteit worden gerealiseerd op deze pitch.

Vooruitgang in halfgeleidertechnologie

CPO-technologie biedt een nieuwe manier om te voldoen aan de steeds grotere prestatie-eisen van AI, met het potentieel om communicatie tussen modules van elektrisch naar optisch te transformeren. Dit versterkt IBM’s lange geschiedenis van leiderschap in halfgeleiderinnovatie, die onder andere de ontwikkeling van de eerste 2 nm node-chip, de introductie van 7 nm en 5 nm procestechnologieën, Nanosheet-transistors, verticale transistors (VTFET), single-cell DRAM en chemisch versterkte fotomaskers omvat.

De ontwerp‑, modellering- en simulatiewerkzaamheden voor CPO werden uitgevoerd in Albany, New York, dat recent werd gekozen door het Amerikaanse ministerie van Handel als de thuisbasis van Amerika’s eerste Nationale Halfgeleidertechnologiecentrum (NSTC), de NSTC EUV Accelerator. Prototypes werden geassembleerd en modules getest in de faciliteit van IBM in Bromont, Quebec, een van de grootste chipassemblage- en testlocaties in Noord-Amerika. Gelegen in de Northeast Semiconductor Corridor tussen de Verenigde Staten en Canada, heeft IBM’s Bromont-fabriek al decennialang de leiding in chipverpakkingstechnologie.

0 reacties